# Structural Optimization of Cryptographic Algorithms Based on Embedded Processor Characteristics

### 2025년

한 성 대 학 교 대 학 원 정보컴퓨터공학과 정보시스템공학전공 권 혁 동

박사학위논문지도교수 서화정

# Structural Optimization of Cryptographic Algorithms Based on Embedded Processor Characteristics

임베디드 프로세서 특성 기반 암호 알고리즘의 구조적 최적화

2024년 12월 일

한 성 대 학 교 대 학 원 정보컴퓨터공학과 정보시스템공학전공 권 혁 동 박사학위논문지도교수 서화정

# Structural Optimization of Cryptographic Algorithms Based on Embedded Processor Characteristics

임베디드 프로세서 특성 기반 암호 알고리즘의 구조적 최적화

위 논문을 공학 박사학위 논문으로 제출함

2024년 12월 일

한 성 대 학 교 대 학 원 정보컴퓨터공학과 정보시스템공학전공

권 혁 동

## 권혁동의 공학 박사학위 논문을 인준함

## 2024년 12월 일

심사위원 <u>박명서</u>(인)

심사위원 김수리(인)

심사위원 이웅희(인)

심사위원 유지현(인)

심사위원 서화정(인)

#### **ABSTRACT**

### Structural Optimization of Cryptographic Algorithms Based on Embedded Processor Characteristics

Kwon, HyeokDong

Major in Information System Engineering

Dept. of Information and Computer Engineering

The Graduate School

Hansung University

This dissertation investigates and presents the results of an optimized implementation technique achieved through modifications to the internal structure of cryptographic algorithms. Among the various aspects of optimal implementation, speed optimization is crucial in improving inefficient computational performance by accelerating the algorithm's processing speed. Parallel implementation is commonly employed for optimization; however, inherent limitations exist when relying solely on parallelizing internal operations. A method for enhancing the performance of cryptographic algorithms is proposed through modifications to their internal structure. These structural

modifications may involve precomputing specific values, utilizing precomputation tables for large-scale calculations, or leveraging processor features to reverse original operations.

The cryptographic algorithms targeted for implementation in this research include the domestic lightweight block cipher CHAM, the lightweight block cipher candidate TinyJAMBU, and the post—quantum cryptography candidate Rainbow. The implementation platforms selected for this study are the 8-bit AVR processor, commonly used in low—end Internet of Things (IoT) environments, and the 64-bit ARM processor, which, though relatively high—end compared to AVR, has recently expanded its application from smartphones to laptops. The proposed technique involves redesigning the internal structure of each algorithm, considering the unique characteristics of the algorithms and the processor environments, to enhance overall algorithm performance.

[Keywords] Block cipher, Post Quantum Cryptography, Optimized implementation, IoT Processor

# Table of Contents

| 1. | Introduction                                          | ••••• | 1   |

|----|-------------------------------------------------------|-------|-----|

|    | 1.1 Main Contribution                                 | ••••• | 1   |

| 2. | Preliminaries                                         | ••••• | 3   |

|    | 2.1 Symmetric-Key Cryptography                        |       | 3   |

|    | 2.2 Public-Key Cryptography                           | ••••• | 5   |

|    | 2.3 Post-Quantum Cryptography                         | ••••• | 6   |

|    | 2.4 Target Cryptographic Algorithms                   | ••••• | 8   |

|    | 2.4.1 Block Cipher CHAM                               |       | 8   |

|    | 2.4.2 Lightweight Cipher TinyJAMBU                    |       | 9   |

|    | 2.4.3 Post-Quantum Cryptography Rainbow               | 1     | . 0 |

|    | 2.5 Target Processors                                 | 1     | . 2 |

|    | 2.5.1 8-bit AVR Microcontroller                       | 1     | . 2 |

|    | 2.5.2 64-bit ARM Processor ·····                      | 1     | . 3 |

|    | 2.6 Previous Works                                    | 1     | . 3 |

| 3. | Optimized Implementation of Target Cipher             | 1     | . 6 |

|    | 3.1 CHAM with Precomputation                          | 1     | . 6 |

|    | 3.1.1 Skip Rounds by Precomputation                   | 1     | . 6 |

|    | 3.1.2 Logical Block Rotation                          | 1     | . 8 |

|    | 3.1.3 Register Scheduling and Instructions Used       | 2     | 20  |

|    | 3.1.4 Alternative Implementation: Furious CHAM        | 2     | 27  |

|    | 3.2 TinyJAMBU with Reverse Bitwise Shift              | 2     | 29  |

|    | 3.2.1 Reverse Bitwise Shift(RBS)                      | 2     | 29  |

|    | 3.2.2 Register Scheduling and Instructions Used       | 3     | 36  |

|    | 3.2.3 Alternative Implementation: Initialization Skip | 4     | 12  |

| 3.3 Rainbow with Look-Up Table Based Multiplication                                                       | 43        |

|-----------------------------------------------------------------------------------------------------------|-----------|

| 3.3.1 Tower-Field Based Multiplication                                                                    | 43        |

| 3.3.2 Look-Up Table Based Multiplication in Rainbow I                                                     | 46        |

| 3.3.3 Resolve of LUT Size Problem in Rainbow III and V                                                    | 50        |

| 3.3.4 Register Scheduling and Instructions Used                                                           | 50        |

| 3.3.5 Alternative Implementation: Avoiding Cache Side Attack                                              | 54        |

| 4. Performance Evaluation                                                                                 | 57        |

| 4.1 Evaluation CHAM Block Cipher                                                                          | 57        |

| 4.2 Evaluation TinyJAMBU Lightweight Cipher                                                               | 59        |

| 4.3 Evaluation Rainbow Post-Quantum Cryptography                                                          | 63        |

| 5. Conclusion                                                                                             | 70        |

| Appendix: Look-Up Table for Rainbow                                                                       | 72        |

| Appendix: Performance evaluation result for Rainbow on A processors                                       | .13<br>80 |

| Appendix: Performance evaluation result for Cache side attaresistance implementation of Rainbow III and V |           |

| Abbreviation: Abbreviation                                                                                | 90        |

| Bibliography                                                                                              | 91        |

| 국문초록                                                                                                      | 95        |

## List of Tables

| [Table 2-1] List of CHAM parameters (n: block size, k: key size, ω:                                |

|----------------------------------------------------------------------------------------------------|

| word size, r: number of rounds) 9                                                                  |

| [Table 2-2] Key and signature size of Rainbow signature. (Key size                                 |

| unit: KB, Signature size unit: bit)                                                                |

| [Table 3-1] List of instructions used in implementation for CHAM in                                |

| alphabetical order ····· 22                                                                        |

| [Table 3-2] Implementation code of proposed CHAM (RC: round                                        |

| counter, RK: round key, X00~X31: plaintext, XT: temporary register,                                |

| Zero: zero register)                                                                               |

| [Table 3-3] Number of keyed permutations each step in tinyJAMBU                                    |

|                                                                                                    |

| [Table 3-4] Pseudocode for keyed permutation(< <n: bitwise="" left<="" td=""></n:>                 |

| shift n times, >>n: bitwise right shift n times,  : bitwise OR, &:                                 |

| bitwise AND, ^: bitwise XOR, ~: bitwise NOT) 30                                                    |

| [Table 3-5] Number of shifts for each implementation                                               |

| [Table 3-6] List of instructions used in implementation for                                        |

| TinyJAMBU in alphabetical order                                                                    |

| [Table 3-7] Implementation code of proposed TinyJAMBU (RC:                                         |

| round counter, RK: round key, X00~X31: plaintext, XT: temporary                                    |

| register, Zero: zero register) 38                                                                  |

| [Table 3-8] Pseudocode of tower-field based polynomial                                             |

| multiplication for Rainbow signature (^: bitwise XOR) 43                                           |

| [Table 3-9] Pseudocode of look-up table based polynomial                                           |

| multiplication for Rainbow I (< <n: bitwise="" left="" n="" shift="" times,="">&gt;n:</n:>         |

| bitwise right shift n times, &: bitwise AND, ^: bitwise XOR) 46                                    |

| [Table 3-10] Pseudocode of look-up table based polynomial                                          |

| multiplication for Rainbow III and V(< <n: bitwise="" left="" n="" shift="" td="" times,<=""></n:> |

| >>n: bitwise right shift n times, &: bitwise AND, ^: bitwise XOR,                                  |

| A: additional) 48                                                   |

|---------------------------------------------------------------------|

| [Table 3-11] List of instructions used to implement Rainbow         |

| signatures in alphabetical order 52                                 |

| [Table $3-12$ ] Implementation code of proposed multiplication (x0: |

| output address, x1: operand address, x2(w2): constant) 53           |

| [Table 3-13] Implementation code of cache side attack resistance    |

| implementation. (x2(w2): constant) 54                               |

| [Table Appendix-1] Precomputation look-up table of tower-field      |

| based polynomial multiplication results on GF16 expressed in        |

| hexadecimal (A: additional table for Rainbow III and V)             |

| [Table Appendix-2] Implementation code of proposed multiplication   |

| for Rainbow III and V (x0: output address, x1: operand address,     |

| x2(w2): constant) 73                                                |

| [Table Appendix-3] Implementation code of constant-time             |

| implementation. (x2(w2): constant)                                  |

# List of Figures

| [Figure 2-1] Symmetric-key cryptography structure 3                     |

|-------------------------------------------------------------------------|

| [Figure 2-2] Block cipher framework (Encryption only) 4                 |

| [Figure 2-3] Stream cipher framework (Encryption only) 5                |

| [Figure 2-4] Public-key cryptography architecture 5                     |

| [Figure 2-5] Round function structure of CHAM                           |

| [Figure 2-6] NLFSR for Keyed permutation of TinyJAMBU 10                |

| [Figure 2-7] Whole structure of TinyJAMBU 10                            |

| [Figure 2-8] Structure of AVR registers                                 |

| [Figure 2-9] Controlling vector registers via arrangement specifiers    |

|                                                                         |

| [Figure $3-1$ ] Flow of counter values in CHAM CTR mode of              |

| operation                                                               |

| [Figure $3-2$ ] Optimized CHAM structure with CTR mode of operation     |

|                                                                         |

| [Figure 3-3] Optimized 32-bit counter CHAM-64/128 structure 20          |

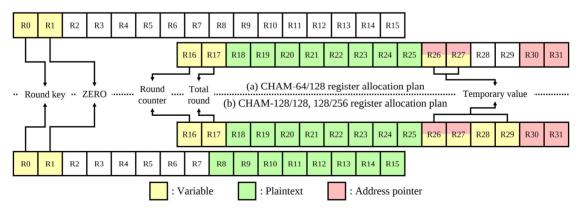

| [Figure 3-4] Register allocation plan for proposed CHAM 20              |

| [Figure 3-5] Two implementation scenarios for the variable key          |

| model                                                                   |

| [Figure 3-6] Register allocation plan for furious CHAM 28               |

| [Figure 3-7] S2 state computation structure using AVR assembly          |

| instructions 31                                                         |

| [Figure 3-8] Proposed RBS applied to s2 state calculation 32            |

| [Figure 3-9] S3 state flow with AVR assembly implementation $\cdots$ 33 |

| [Figure 3-10] S3 state calculation with RBS technique applied 33        |

| [Figure 3-11] Operation process with the previous s1 state block        |

| operation and RBS applied                                               |

| [Figure 3-12] Operate s2 state block with single shift 35               |

| [Figure 3-13] Register allocation plan for RBS TinyJAMBU 36             |

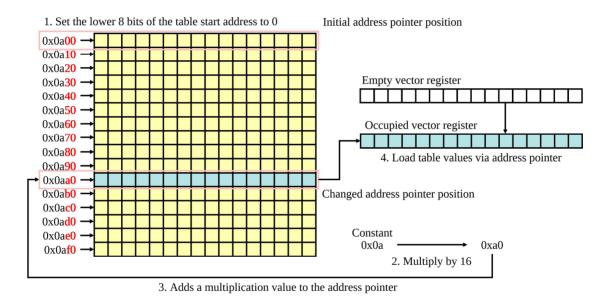

| [Figure 3-14] Table loading process in proposed Rainbow signature 46            |

|---------------------------------------------------------------------------------|

| [Figure 3-15] Register allocation plan for Look-up table based                  |

| Rainbow signature                                                               |

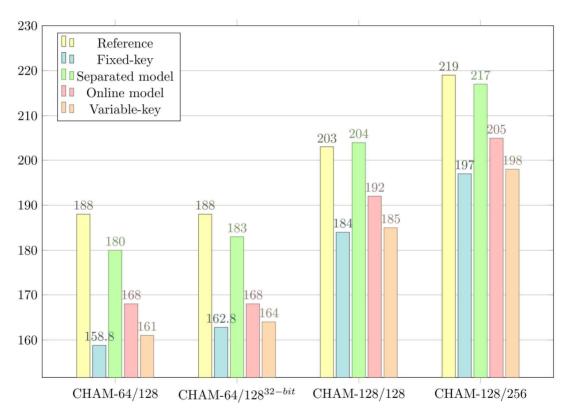

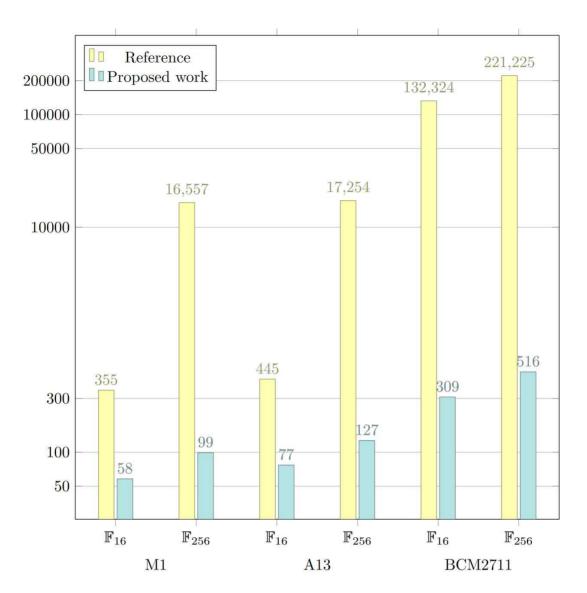

| [Figure 4-1] Performance Measurement Results for CHAM (Unit:                    |

| clock cycles per byte, 32-bit: 32-bit counter of CHAM-64/128) $\cdots$ 57       |

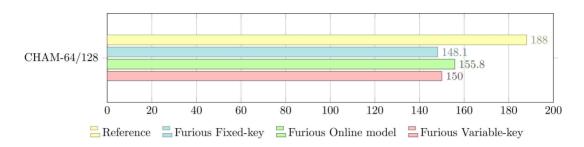

| [Figure 4-2] Performance Measurement Results for Furious                        |

| CHAM-64/128 (Unit: clock cycles per byte) 59                                    |

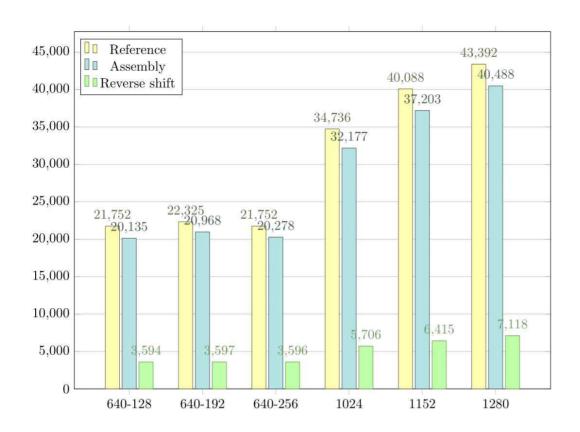

| [Figure 4-3] Performance Measurement Results for Keyed                          |

| permutation of TinyJAMBU (Unit: clock cycles)                                   |

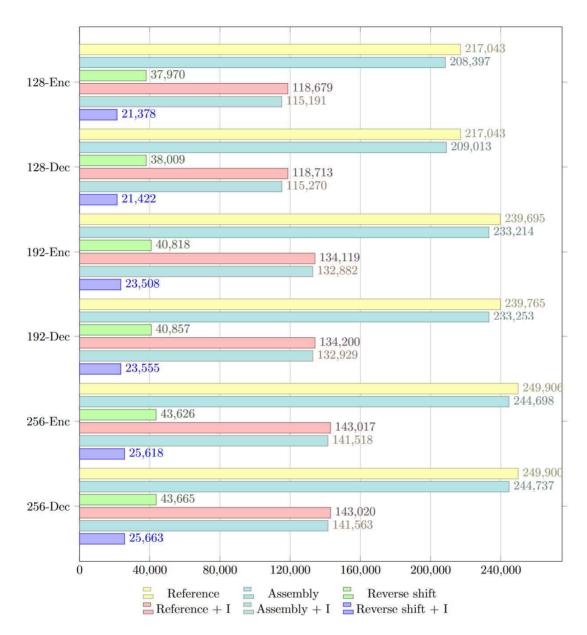

| [Figure 4-4] Performance Measurement Results for TinyJAMBU                      |

| (Unit: clock cycles, I: Initialization skip implementation) 62                  |

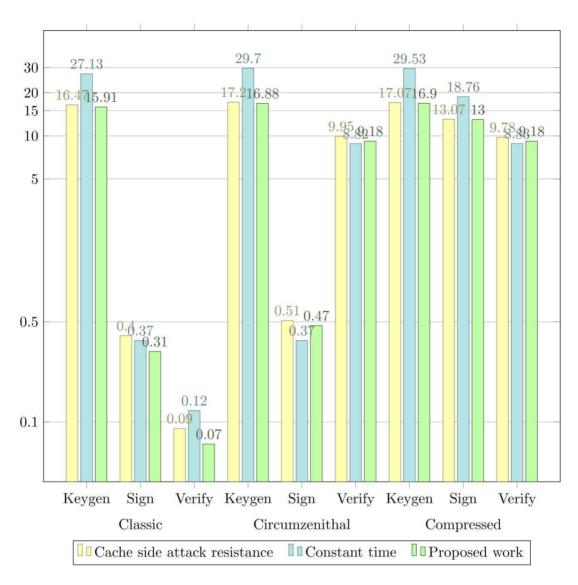

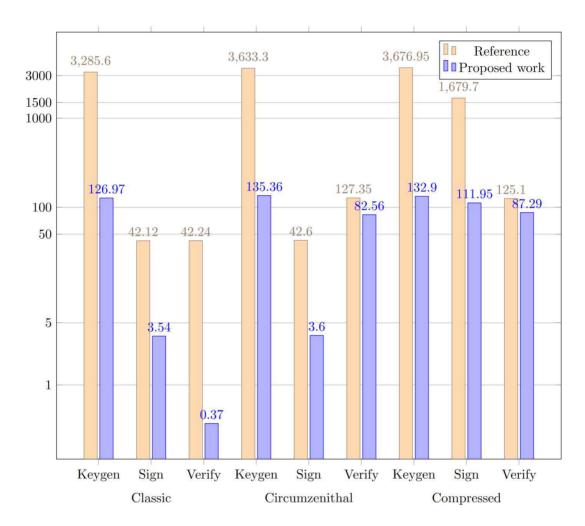

| [Figure 4-5] Performance Measurement Results for table based                    |

| multiplier of proposed Rainbow signature in log scale (Unit: clock              |

| cycles) 64                                                                      |

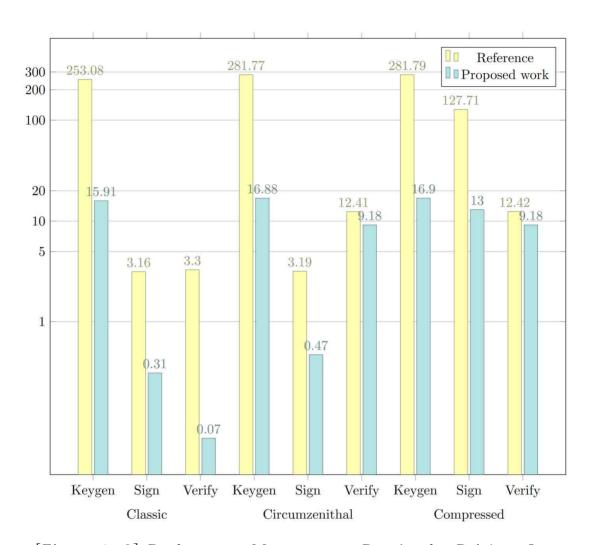

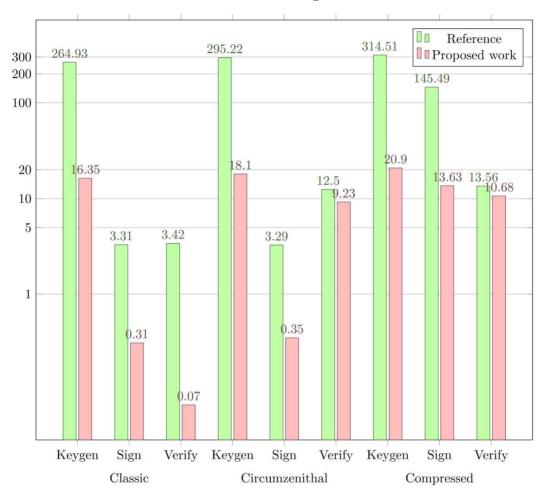

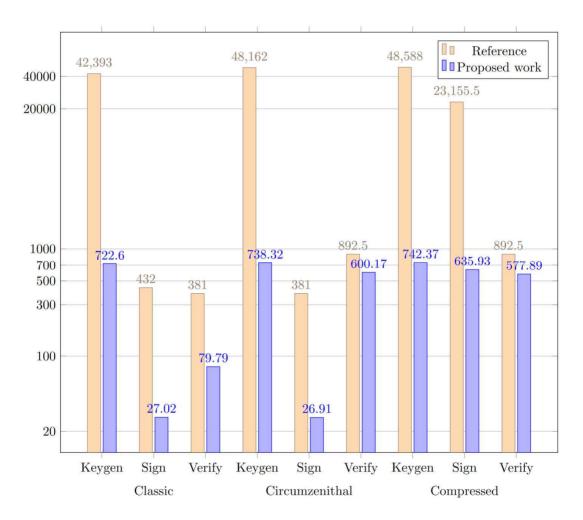

| [Figure 4-6] Performance Measurement Results for Rainbow I on Apple             |

| M1 processors expressed in log scale (Unit: 10 <sup>6</sup> clock cycles) 65    |

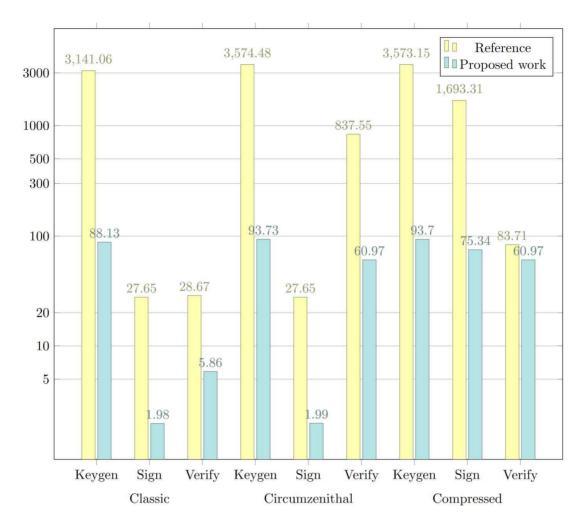

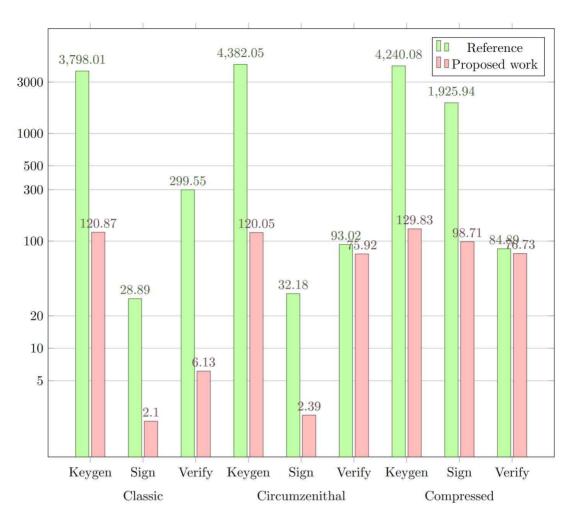

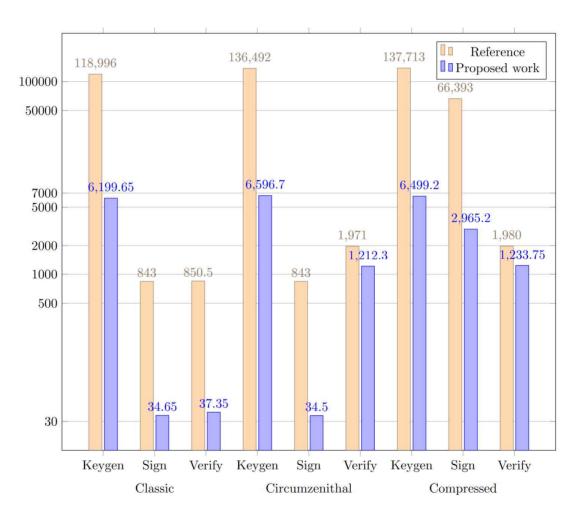

| [Figure 4-7] Performance Measurement Results for Rainbow III on Apple           |

| M1 processors expressed in log scale (Unit: 10 <sup>6</sup> clock cycles)       |

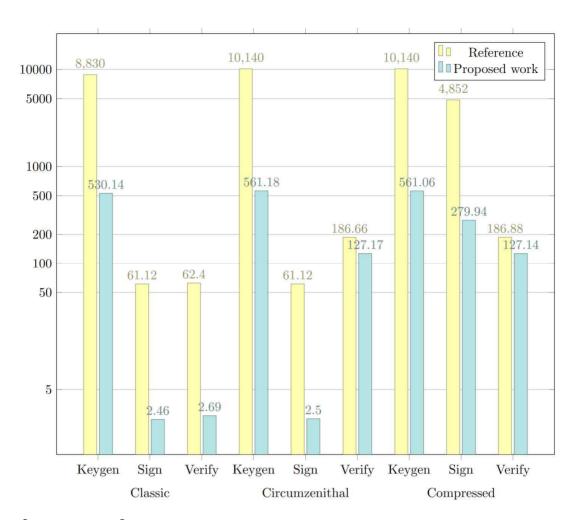

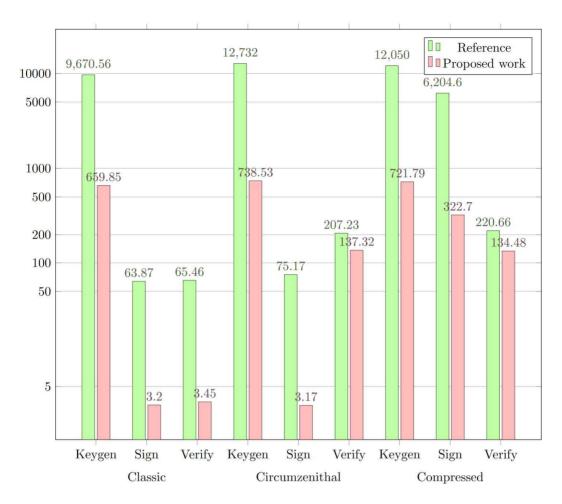

| [Figure 4-8] Performance Measurement Results for Rainbow V on Apple             |

| M1 processors expressed in log scale (Unit: 10 <sup>6</sup> clock cycles) 67    |

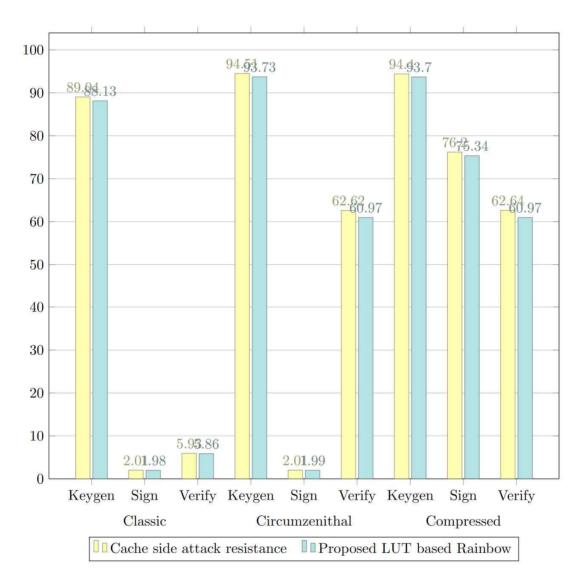

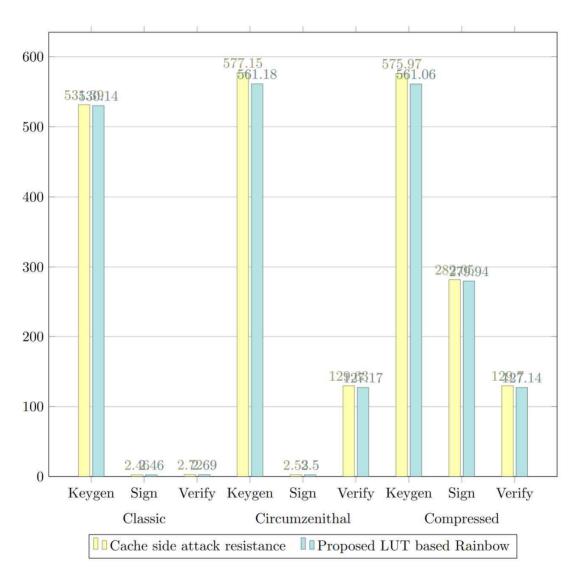

| [Figure 4-9] Performance Measurement Results for Rainbow I cache                |

| side attack resistance implementation and constant-time                         |

| implementation on Apple M1 processors expressed in log scale (Unit:             |

| $10^6$ clock cycles) 68                                                         |

| [Figure Appendix-1] Performance Measurement Results for Rainbow                 |

| I on Apple A13 processors expressed in log scale (Unit: $10^6$ clock            |

| cycles)                                                                         |

| [Figure Appendix-2] Performance Measurement Results for Rainbow                 |

| III on Apple A13 processors expressed in log scale (Unit: 10 <sup>6</sup> clock |

| cycles) 81                                                                    |

|-------------------------------------------------------------------------------|

| [Figure Appendix-3] Performance Measurement Results for Rainbow               |

| V on Apple A13 processors expressed in log scale (Unit: 10 <sup>6</sup> clock |

| cycles)                                                                       |

| [Figure Appendix-4] Performance Measurement Results for Rainbow               |

| I on BCM2711 processors expressed in log scale (Unit: 10 <sup>6</sup> clock   |

| cycles) 83                                                                    |

| [Figure Appendix-5] Performance Measurement Results for Rainbow               |

| III on BCM2711 processors expressed in log scale (Unit: 10 <sup>6</sup> clock |

| cycles)                                                                       |

| [Figure Appendix-6] Performance Measurement Results for Rainbow               |

| V on BCM2711 processors expressed in log scale (Unit: 10 <sup>6</sup> clock   |

| cycles) 85                                                                    |

| [Figure Appendix-7] Performance Measurement Results for Rainbow               |

| III cache side attack resistance implementation on Apple M1                   |

| processors (Unit: 10 <sup>6</sup> clock cycles)                               |

| [Figure Appendix-8] Performance Measurement Results for Rainbow               |

| V cache side attack resistance implementation on Apple M1                     |

| processors (Unit: 10 <sup>6</sup> clock cycles)                               |

#### 1. Introduction

#### 1.1 Main Contribution

Cryptographic algorithms, which provide security based on complex mathematical principles, typically require significant computational resources. With recent advancements in hardware, performing cryptographic operations is no longer a major challenge. However, for small electronic devices such as sensor nodes, available resources are limited. and executing cryptographic algorithms can consume considerable time. This dissertation presents optimal implementation methods to efficiently execute cryptographic algorithms. Although there are various perspectives on optimal implementation, the focus is primarily on speed optimization, which aims to enhance processing speed. The main contributions of this dissertation are as follows.

1. Proposal of optimized implementation through modifications to the internal operational structure of the algorithm. Parallel implementation is one of the most powerful methods used in optimization; however, it is limited to environments that support parallel instructions. Moreover, parallel implementation is applicable only to algorithms that benefit from parallel operations. Therefore, various methods for modifying the internal structure of algorithms are proposed. By utilizing the unique characteristics of each algorithm, the computational process is redesigned, and a more advanced design is proposed by taking into account the characteristics of the processor.

2. Presentation of additional implementations for special purposes. The proposed optimized implementations are designed based on general use cases. In addition, specialized implementations tailored to specific scenarios are presented. While these additional implementations may require certain assumptions not present in the general implementations, they offer more optimized performance or exhibit resistance to certain attacks, thereby possessing distinctive features compared to the general optimal implementations.

The remainder of this dissertation is organized as follows. Chapter 2 introduces various cryptographic algorithm structures and examines the algorithms selected for optimal implementation, along with an introduction to the target processors for optimization. Additionally, prior research on optimal implementations is reviewed. Chapter 3 discusses the redesign for optimal implementation, the methods for algorithm implementation, and additional implementations. Chapter 4 evaluates the performance of the proposed implementations. Chapter 5 concludes the dissertation.

### 2. Preliminaries

#### 2.1 Symmetric-Key Cryptography

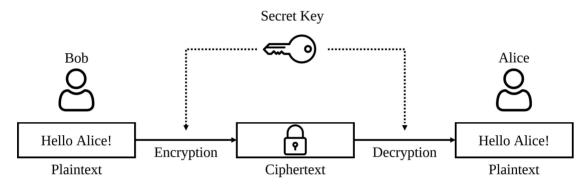

A symmetric-key encryption system is an algorithm in which encryption and decryption are performed using a single shared secret key, also referred to as a secret-key encryption algorithm. The basic structure of symmetric-key cryptography is shown in [Figure 2-1].

[Figure 2-1] Symmetric-key cryptography structure

It is defined by the use of the same key for both encryption and decryption. However, symmetric-key cryptography has the drawback of difficulty in securely sharing the secret key. Since the secret key encryption and decryption, if the used for both key is confidential information compromised, the encrypted can be immediately restored. Therefore, securely sharing the secret key is critical. and this remained a significant challenge until development of public-key cryptography. Algorithms that belong to symmetric key encryption include DES, AES, LEA, ARIA, and CHAM.

Symmetric-key cryptography is divided into block ciphers and stream ciphers.

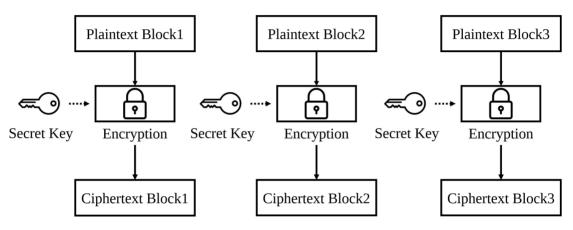

• A block cipher encrypts data in fixed-size blocks, and its structure is illustrated in [Figure 2-2]. Since input messages may exceed the block size, block cipher operation modes are provided to encrypt messages larger than a single block. While block ciphers offer high diffusion and versatility, they tend to have slower encryption speeds and the propagation of errors in case of transmission issues. Common operation modes include ECB, CBC, CFB, OFB, and CTR.

[Figure 2-2] Block cipher framework (Encryption only)

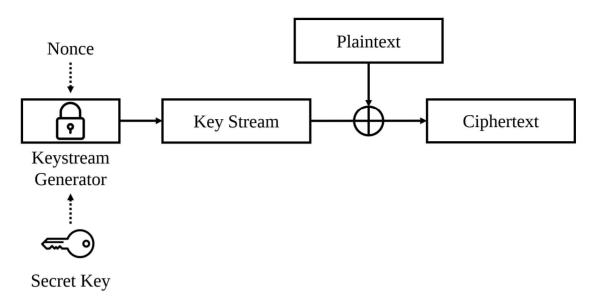

• Stream ciphers, on the other hand, do not encrypt the input message directly. Instead, they generate pseudorandom numbers, which are combined with the input message to produce the ciphertext, as shown in [Figure 2-3]. Typically, XOR operations are used to combine the pseudorandom numbers with the input message. Stream ciphers are known for their fast encryption speed and the non-propagation of errors, but they suffer from lower diffusion.

[Figure 2-3] Stream cipher framework (Encryption only)

#### 2.2 Public-Key Cryptography

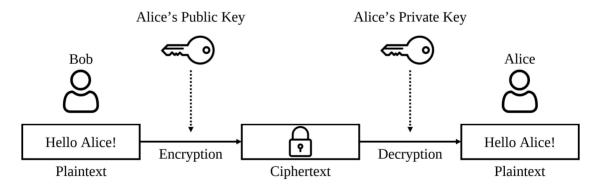

A public-key encryption system uses different keys for encryption and decryption, as shown in [Figure 2-4], and is therefore also referred to as an asymmetric-key encryption algorithm.

[Figure 2-4] Public-key cryptography architecture

In this cryptography, encryption is performed using a public key, while decryption is carried out using a private key, also known as a secret key. The public key is known to all participants in the

network, but only the key owner knows the private key. As long as the private key remains secure, decrypting the ciphertext is impossible, making public—key encryption highly secure for transmitting information or messages. Due to these characteristics, public—key encryption can also provide additional functionalities such as authentication, integrity, and non—repudiation. However, compared to symmetric—key encryption, it is significantly slower and requires larger key sizes. For this reason, public—key encryption is not commonly used for general message transmission but is instead employed for tasks such as key exchange and authentication. Examples of public—key cryptography include RSA.

#### 2.3 Post-Quantum Cryptography

With the advancement of quantum computing, cryptographic systems based on traditional mathematical challenges have begun to face threats. Grover's algorithm, which can be implemented on quantum computers, is an optimized search algorithm capable of performing attacks such as brute force effectively. While Grover's algorithm poses a threat to symmetric—key cryptography and hash functions, increasing the key length can mitigate its impact. Shor's algorithm, on the other hand, solves problems such as integer factorization and discrete logarithms. Among public—key cryptography, those based on integer factorization, such as RSA, are highly vulnerable to Shor's algorithm, and no effective countermeasures are currently known.

In response to the threat posed by quantum computers, the U.S. National Institute of Standards and Technology (NIST) launched a competition to standardize new cryptographic algorithms resistant to quantum attacks, known as post-quantum cryptography (PQC). As a

result, Kyber was selected as the standard for PKE/KEM algorithms, while Dilithium, Falcon, and SPHINCS+ were chosen for digital signature algorithms. In Republic of Korea, a competition named KpqC is being held to select a PQC standard. Currently, the competition is in its second round, with NTRU+, PALOMA, REDOG, and SMAUG-T competing as candidates for PKE/KEM, and AIMer, HAETAE, MQ-Sign, and NCC-Sign competing in the digital signature category. Post-quantum cryptography involves more fundamental problems than traditional symmetric-key and public-key cryptography.

- Lattice—based cryptography: It is based on the Shortest Vector Problem (SVP) and Closest Vector Problem (CVP), which involve finding the shortest vector in a lattice when two integer vectors exist. Lattice—based cryptography is known for its fast computation speed and relatively small key and signature sizes. Due to these advantages, many algorithms in the post—quantum cryptography competition are based on lattice problems. Examples of lattice—based cryptographic algorithms include Kyber, Dilithium, Falcon, NCC—Sign, and HAETAE.

- Code-based cryptography: This problem generates public/private key pairs using error correction codes, which control errors in signals. Code-based cryptography has been subject to security analysis for a longer time compared to other hard problems, thus earning a high level of trust. Classic McEliece is a representative example of code-based cryptography.

- Hash-based cryptography: It relies on the collision resistance of hash functions. Although quantum algorithms can compromise hash functions, security can be maintained by extending the hash output length. Additionally, if a security vulnerability is discovered in a

hash function used in the cryptographic scheme, it can be replaced with another hash function to maintain security. SPHINCS+ is an example of hash-based cryptography.

• Multivariate based cryptography: This cryptographic method is based on the difficulty of solving systems of multivariate polynomial equations over finite fields. Compared to other problems, proving security mathematically is relatively straightforward. Since the primary operation involves solving matrices of polynomials, effective implementations can be achieved using the Gaussian Elimination algorithm. Rainbow and MQ-Sign are examples of multivariate polynomial cryptography.

#### 2.4 Target Cryptographic Algorithm

#### 2.4.1 Block Cipher CHAM

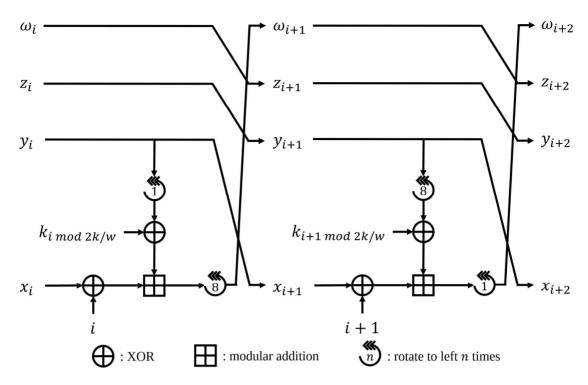

CHAM is a block cipher introduced in South Korea in 2017, designed with low—end processors in mind. In 2019, revised CHAM was published, with the only difference between the original and revised versions being the number of rounds, while the core design remains the same. CHAM is an ARX—based algorithm that divides the input data into four blocks, as shown in [Figure 2–5]. Although the operations per round are identical, the number of left shifts differs between odd and even rounds. [Table 2–1] summarizes the parameters of CHAM.

[Figure 2-5] Round function structure of CHAM

[Table 2-1] List of CHAM parameters (n: block size, k: key size, ω: word size, r: number of rounds)

| Cipher       | n   | k   | ω  | r   |

|--------------|-----|-----|----|-----|

| CHAM-64/128  | 64  | 128 | 16 | 88  |

| CHAM-128/128 | 128 | 128 | 32 | 112 |

| CHAM-128/256 | 128 | 256 | 32 | 120 |

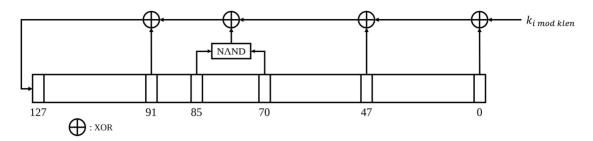

#### 2.4.2 Lightweight Cipher TinyJAMBU

TinyJAMBU is a permutation—based variant of the block cipher JAMBU. The encryption and decryption processes consist of five stages: Initialization, Processing Associated Data, Encryption/Decryption, Finalization, and Verification. TinyJAMBU employs a keyed permutation structure with NLFSR, as shown in

[Figure 2-6], and [Figure 2-7] shows the TinyJAMBU mode. [Table 2-2] provides its pseudocode representation.

[Figure 2-6] NLFSR for Keyed permutation of TinyJAMBU

[Figure 2-7] Whole structure of TinyJAMBU

#### 2.4.3. Post Quantum Cryptography Rainbow

Rainbow, a finalist in the third round of the NIST post-quantum cryptography competition, is a multivariate polynomial-based digital signature algorithm. It leverages the UOV problem and offers faster

signing and verification speeds compared to other algorithms, along with smaller signature sizes. However, Rainbow has the disadvantage of slow key generation and significantly larger key sizes than other post—quantum algorithms, especially lattice—based cryptography. Variants of Rainbow, such as the circumzenithal and compressed versions, are available to reduce key size, and the parameters are summarized in [Table 2-2].

[Table 2-2] Key and signature size of Rainbow signature. (Key size unit: KB, Signature size unit: bit)

| Security<br>Level     | Parameters         | Public<br>key size | Private<br>key size  | Signature<br>size |

|-----------------------|--------------------|--------------------|----------------------|-------------------|

| Standard              | l Rainbow          |                    |                      |                   |

| I                     | (GF(16),36,32,32)  | 157.8              | 101.2                | 528               |

| III                   | (GF(256),68,32,48) | 681.4              | 611.3                | 1,312             |

| V                     | (GF(256),96,36,64) | 1,885.4            | 1,375.7              | 1,632             |

| Circumzenital Rainbow |                    |                    |                      |                   |

| I                     | (GF(16),36,32,32)  | 58.8               | 101.2 (99.0)         | 528               |

| III                   | (GF(256),68,32,48) | 258.4              | 611.3<br>(603.0)     | 1,312             |

| V                     | (GF(256),96,36,64) | 523.5              | 1,357.7<br>(1,631.8) | 1,696             |

#### 2.5 Target Processor

#### 2.5.1 8-bit AVR Microcontroller

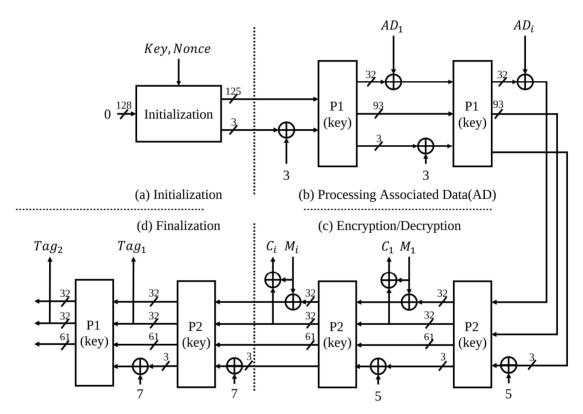

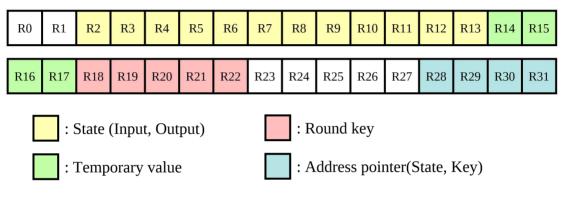

The 8-bit AVR processor, first introduced in 1996 with the ATmega series, is a RISC-based processor. It features 32 general-purpose 8-bit registers, and for any operation, values must first be loaded from memory into the registers. Similarly, the results of operations must be stored back from the registers to memory, with each process requiring 2 cycles. [Figure 2-8] illustrates the structure of AVR registers.

[Figure 2-8] Structure of AVR registers

The R1 register serves as the zero register, allowing flexible use, but it must always hold the value zero when the operation is complete. Therefore, if the R1 register is used, it is recommended to clear the register with the CLR instruction before the operation finishes. Registers R2 through R17, as well as R28 and R29, are callee—saved registers. These registers might hold important values necessary for computations prior to function calls, so their contents should be temporarily saved before usage and restored after the operation. Lastly, registers R26 through R31 are pointer registers, with R26 and R27, R28 and R29, and R30 and R31 paired to form the X, Y, and Z pointer registers. These pointer registers are used to access memory, either to load or store values via pointers. It is

important to note that since the Y pointer register is callee—saved, its value needs to be preserved before use.

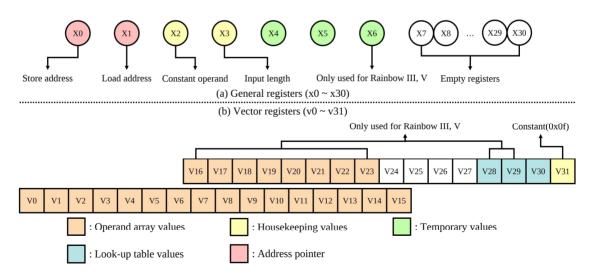

#### 2.5.2 64-bit ARM Processor

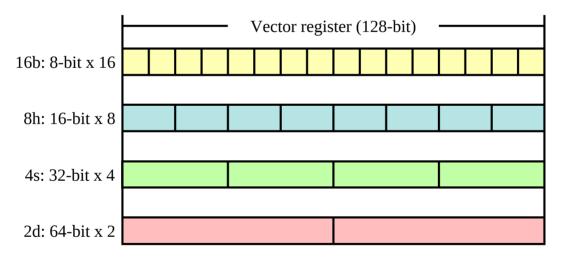

The ARMv8 processor is a high-performance processor within the embedded processor category, commonly used in devices such as smartphones and laptops. Its register configuration consists of 64-bit general-purpose registers and 128-bit vector registers. The vector registers, which support parallel computation, have a maximum size of 128 bits, though the effective size for storage is limited to 64 bits, allowing for up to two values to be stored. The arrangement specifier determines how the internal data is treated in terms of bit size, which can be set when utilizing vector instructions (also referred to as NEON). [Figure 2-9] illustrates how data is handled in vector registers based on the arrangement specifier.

[Figure 2-9] Controlling vector registers via arrangement specifiers

#### 2.6 Previous Work

Seo et al. conducted optimized implementations of the LEA and HIGHT block ciphers on an 8-bit AVR processor. For this purpose, they optimized the rotation operations, particularly the right rotation, by utilizing BST and BLD instructions to reduce the number of instructions used. Additionally, they addressed the limited number of registers available on the AVR processor by optimizing register usage strategies. As a result, the C implementation of LEA required 326 cpb for key generation, 263 cpb for encryption, and 236 cpb for decryption, whereas the AVR-optimized implementation achieved 235, 168, and 176 cpb for the same processes, respectively. For HIGHT, the C implementation required 156, 537, and 525 cpb for key generation, encryption, and decryption, while the AVR-optimized implementation achieved 58, 160, and 161 cpb, respectively.

Kim et al. proposed the FACE-LIGHT algorithm, a lightweight implementation of AES-CTR mode tailored for low-resource processors like AVR. Their approach involved designing a new cache table to enable partial precomputation, extending the precomputation capability from two rounds in the original FACE algorithm to three rounds in FACE-LIGHT. The resulting implementation achieved optimal performance, with AES-128, AES-192, and AES-256 requiring 1,967, 2,449, and 2,931 cpb, respectively.

Kwon et al. optimized the block cipher SIMON for the AVR processor. Their work leveraged the characteristics of 8-bit processors to demonstrate that specific registers could precomputed. They also calculated operational parts based on the plaintext length. The implementation resulted in performance improvements ranging from 1.5% to 5.3%.

Seo et al. also optimized the post-quantum cryptographic algorithms SIDH and SIKE on the ARMv8 processor. Their approach

focused on accelerating the Montgomery multiplier and extensively utilized 64-bit operations. For SIDH, the C implementation required 643.8 million or 574.3 million clock cycles, depending on the processor, while the proposed method reduced this to 133.3 million and 90.3 million clock cycles, respectively. For SIKE, the C implementation required 626.3 million or 558.5 million clock cycles, but the optimized implementation reduced this to 129.6 million and 87.8 million clock cycles, respectively.

Kim et al. optimized the post-quantum signature scheme CRYSTALS-Dilithium for ARM processors. Their proposed method utilized ARM NEON parallel instructions to optimize the NTT multiplier and employed layer merging to reduce memory access frequency. This approach resulted in performance improvements of 49%, 113%, and 41% in the key generation, signature generation, and verification processes, respectively.

### 3. Optimized Implementation of Target Cipher

#### 3.1 CHAM with Precomputation

#### 3.1.1 Skip Rounds by Precomputation

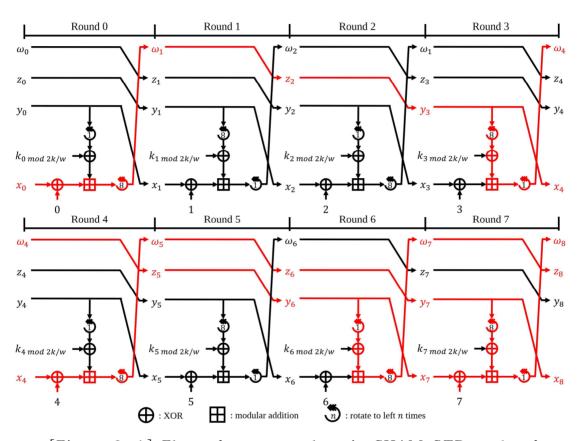

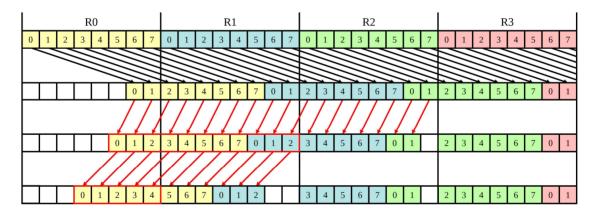

In the Counter (CTR) mode of operation, rather than encrypting the plaintext directly, a fixed nonce is first encrypted, and the result is then XORed with the plaintext to perform the encryption. The nonce is divided into a fixed part, generated randomly, and a counter that represents the block number. Since the fixed part remains the same for all blocks, it always produces the same result, making precomputation possible. Due to the structure of CHAM's round function, as the encryption progresses, the block storing the counter begins to affect other blocks, making it necessary to analyze the flow of the counter block. [Figure 3–1] highlights the flow of counter values in each round, marked in red.

In round 0, only one block is affected by the counter, but by round 9, all blocks are influenced by the counter. This implies that certain computations during the first nine rounds can be omitted. However, for the sake of implementation efficiency, the actual precomputations are conducted up to the first eight rounds. This corresponds to approximately 9.09%, 7.14%, and 6.67% of the total rounds for CHAM's 88, 112, and 120-round variants, respectively. The specific computations that can be omitted for each round are as follows:

- Round 0: Addition of the round key to the second block.

- Round 1: Entire round.

- Round 2: Entire round.

- Round 3: Addition of the round counter to the first block.

- Round 4: Addition of the round key to the second block (same as

round 0).

- Round 5: Entire round.

- Round 6: Addition of the round counter to the first block (same as round 3).

- Round 7: No precomputable operations.

[Figure 3-1] Flow of counter values in CHAM CTR mode of operation

Although [Figure 3-1] shows that precomputations are possible in round 8, they were not implemented. Implementing round 8 results in less than 1 cpb performance improvement. However, due to the paired round structure of CHAM, implementing round 9 separately would lead to inefficiency, and thus, round 8 is not implemented.

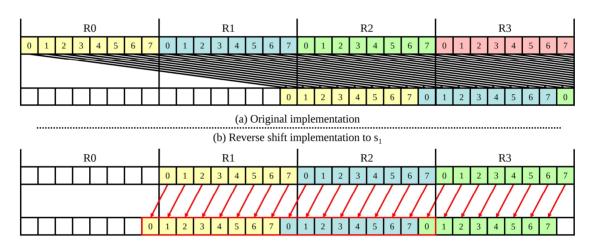

#### 3.1.2 Logical Block Rotation

At the end of each round in CHAM, the blocks undergo a word—wise rotation. In CHAM—64/128, the rotation occurs in 16—bit units, while for the other CHAM variants, the rotation occurs in 32—bit units. Although the block rotation can be implemented in AVR assembly using the MOV instruction, a more efficient implementation can be achieved using the MOVW instruction, which moves data in 16—bit word units. However, the implementation can be further optimized by applying a logical block rotation, thereby omitting the actual rotation.

Also in CHAM, the blocks used for computation in each round are the first and second blocks. Since the block rotation occurs at the end of every round, the blocks involved in computations do not change. Without performing the rotation, the first and second blocks are used in the first round, the second and third blocks in the second round, the third and fourth blocks in the third round, and the fourth and first blocks in the fourth round. This process repeats starting from the fifth round. Thus, the original implementation grouped odd and even rounds in pairs, but by applying logical block rotation, the implementation can be optimized into 4-round units. This is also the reason why round 8 was not implemented in Section 3.1.1; implementing round 8 would require separate implementation for rounds 9, 10, and 11, making efficient implementation more difficult.

A similar approach can be applied to the 8-bit left rotation operation used in each round. Since the AVR registers store 8 bits, the 8-bit left rotation can be implemented using register shifting instructions instead of a rotation instruction. However, instead of actually shifting the registers, the operation can be logically treated as if the value has been rotated. In the following round, operations

that would normally apply to the lower register can be applied to the upper register, effectively bypassing the rotation operation.

[Figure 3-2] illustrates the structure of the first eight rounds of CHAM with all proposed techniques applied.

[Figure 3-2] Optimized CHAM structure with CTR mode of operation

In block cipher counter mode, a 16-bit counter can be used, but a 32-bit counter is generally preferred. In CHAM-64/128, where internal blocks are processed in 16-bit units, the structure of a 16-bit counter is depicted in [Figure 3-2]. If a 32-bit counter is used, two blocks are required to store the counter value, resulting in a slightly different structure as shown in [Figure 3-3]. No additional implementation is required for CHAM-128/128 and CHAM-128/256, as they operate with 32-bit units.

[Figure 3-3] Optimized 32-bit counter CHAM-64/128 structure

3.1.3 Register Scheduling, Instructions Used and Implementation

To implement the proposed CHAM cipher, the register allocation is

planned as shown in [Figure 3-4].

[Figure 3-4] Register allocation plan for proposed CHAM

Register R0 is used to store the round key value, while R1 serves

as a zero register. In AVR architecture, R1 is conventionally assigned as the zero register by default, so there is no need to use another register. Register R16 holds the total round count for CHAM, with 88 rounds for CHAM-64/128, 112 for CHAM-128/128, and 120 for CHAM-128/256. Register R17 is used to store the present round counter value, which increments with each round. Registers R18 through R25 store the plaintext composed of the nonce and counter. Lastly, registers R26 and R27, R30 and R31 are used both as the X, Z register, respectively. And also R26 and R27 are used for temporary registers to store intermediate values during computations. In case of CHAM-128/128 and CHAM-128/256, these are required more plaintext registers and temporary registers. So in this cases, R8 to R15 used to store plaintext and R28, R29 used for additional temporary registers.

3 - 11the [Table summarizes instructions used in the implementation, while [Table 3-2] shows the code for the first 8 rounds where round skipping applied, specifically is for CHAM - 64/128.

[Table 3-1] List of instructions used in implementation for CHAM in alphabetical order

| Mnemonic | Operands | Description            | Operation  |

|----------|----------|------------------------|------------|

| ADC      | Rd, Rr   | Add with Carry         | Rd←Rd+Rr+C |

| ADD      | Rd, Rr   | Add without Carry      | Rd←Rd+Rr   |

| EOR      | Rd, Rr   | Exclusive OR           | Rd←Rd⊕Rr   |

| I D      | Da Vi    | Load Indirect and Post | Rd←(X)     |

| LD       | Rd, X+   | Increment              | X←X+1      |

| LD        | Rd, Y+              | Load Indirect and Post  | Rd←(Y)                     |

|-----------|---------------------|-------------------------|----------------------------|

| -,        |                     | Increment               | Y←Y+1                      |

| LD Rd, Z+ |                     | Load Indirect and Post  | Rd←(Z)                     |

| LD        | Rd, Z+              | Increment               | Z <b>←</b> Z+1             |

| LDI       | Rd, K               | Load Immediate          | Rd←K                       |

| LPM       | Rd, Z               | Load Program Memory     | Rd←(Z)                     |

|           |                     |                         | $Rd(n+1) \leftarrow Rd(n)$ |

| LSL       | Rd                  | Logical Shift Left      | Rd(0)←0                    |

|           |                     |                         | C←Rd(7)                    |

| MOV       | Rd, Rr              | Copy Register           | Rd←Rr                      |

| MOVW      | Rd, Rr              | Copy Register Word      | Rd+1:Rd←Rr+1:Rr            |

| POP       | Rd                  | Pop Register from Stack | Rd←STACK                   |

| PUSH      | Rr                  | Push Register on Stack  | STACK←Rr                   |

|           |                     | Dotate Left Through     | $Rd(n) \leftarrow Rd(n+1)$ |

| ROL       | Rd                  | Rotate Left Through     | Rd(7)←0                    |

|           |                     | Carry                   | C←Rd(0)                    |

| СТ        | V ± D,,             | Store Indirect and Post | (X)←Rr                     |

| 51        | ST X+, Rr Increment |                         | (X)←X+1                    |

| СТ        | V ± D.,             | Store Indirect and Post | (Y)←Rr                     |

| ST        | Y+, Rr              | Increment               | (Y)←Y+1                    |

| СТ        | Y+, Rr              | Store Indirect and Post | (Z)←Rr                     |

| ST        |                     | Increment               | (∑)←Z+1                    |

Lines 1-4 represent round 0, where the LDI instruction is used to retrieve precomputed values from the second block and add them to the first block containing the counter value. Rounds 1 and 2 are skipped and do not appear in the code. Lines 5-18 correspond to

[Table 3-2] Implementation code of proposed CHAM (RC: round counter, RK: round key, X00~X31: plaintext, XT: temporary register, Zero: zero register)

| Line |      | Code |      | Comment                              |

|------|------|------|------|--------------------------------------|

| 1:   | LDI  | XTO, | 0x45 | Round 0 start                        |

| 2:   | LDI  | XT1, | 0x65 |                                      |

| 3:   | ADD  | X00, | XT0  |                                      |

| 4:   | ADC  | X01, | XT1  | ROL8 skipped                         |

| 5:   | ADIW | R30, | 6    | Round 3 start                        |

| 6:   | MOVW | XTO, | X00  |                                      |

| 7:   | LD   | RK,  | Z+   |                                      |

| 8:   | EOR  | XTO, | RK   |                                      |

| 9:   | LD   | RK,  | Z+   |                                      |

| 10:  | EOR  | XT1, | RK   |                                      |

| 11:  | LDI  | X30, | 0x65 |                                      |

| 12:  | LDI  | X31, | 0x77 |                                      |

| 13:  | ADD  | X30, | XT0  |                                      |

| 14:  | ADC  | X31, | XT1  |                                      |

| 15:  | LSL  | X30  |      |                                      |

| 16:  | ROL  | X31  |      |                                      |

| 17:  | ADC  | X30, | ZERO |                                      |

| 18:  | LDI  | RC,  | 4    |                                      |

| 19:  | EOR  | X01, | RC   | Round 4 start, XOR on upper register |

| 20:  | LDI  | XTO, | 0xDC |                                      |

| 21:  | LDI  | XT1, | 0xCA |                                      |

| 22:  | ADD  | X01, | XT0  | XOR in reverse order of registers    |

| 23:  | ADC  | X00, | XT1  | XOR in reverse order of registers    |

| 24:  | LDI  | X10, | 0x02 | Round 5 start                        |

| 25: | LDI  | X11, | 0X32       |                                    |

|-----|------|------|------------|------------------------------------|

| 26: | ADIW | R30, | 4          | Round 6 start                      |

| 27: | MOVW | XTO, | X30        |                                    |

| 28: | LSL  | XT0  |            |                                    |

| 29: | ROL  | XT1  |            |                                    |

| 30: | ADC  | XTO, | ZERO       |                                    |

| 31: | LD   | RK,  | Z+         |                                    |

| 32: | EOR  | XTO, | RK         |                                    |

| 33: | LD   | RK,  | <u>Z</u> + |                                    |

| 34: | EOR  | XT1, | RK         |                                    |

| 35: | LDI  | X20, | 0x0B       | Load in reverse order of registers |

| 36: | LDI  | X21, | 0x3D       | Load in reverse order of registers |

| 37: | ADD  | X21, | XT0        |                                    |

| 38: | ADC  | X20, | XT1        |                                    |

| 39: | LDI  | RC,  | 7          |                                    |

| 40: | MOVW | XTO, | X00        | Round 7 start                      |

| 41: | EOR  | X30, | RC         |                                    |

| 42: | LD   | RK,  | Z+         |                                    |

| 43: | EOR  | XT1, | RK         |                                    |

| 44: | LD   | RK,  | Z+         |                                    |

| 45: | EOR  | XTO, | RK         |                                    |

| 46: | ADD  | X30, | XT1        |                                    |

| 47: | ADC  | X31, | XT0        |                                    |

| 48: | LSL  | X30  |            |                                    |

| 49: | ROL  | X31  |            |                                    |

| 50: | ADC  | X30, | ZERO       |                                    |

| 51: | INC  | RC   |            |                                    |

round 3, where the ADIW instruction first shifts the lower address of the skipped round key, followed by normal operations, with lines 11-12 fetching precomputed values. The round counter, which had not been modified until this point, is updated at line 18. Lines 19-23 implement round 4, which is nearly identical to round 0, except that an XOR operation is performed with the round counter before the computation begins. In round 0, XOR with 0 would yield the same result, so it was omitted, but round 4 requires XOR due to the round counter.

Lines 24-25 implement round 5, which, like rounds 1 and 2, can be fully skipped. However, a load operation is added, as the values are needed for round 6. Lines 26-39 represent round 6, structured similarly to round 3. Finally, the implementation of round 7 in lines 40-51 completes the process, as no further parts can be skipped.

Since logical block rotation, described in section 3.1.2, is applied, no word-level rotation occurs at the end of each round. The eight left-rotate operations are also omitted in lines 4, 19, 22, 23, 35, and 36. These rotations would have required the MOV instruction and an additional temporary register, necessitating a total of three MOV instructions, which were successfully avoided. CHAM-128/128 and CHAM-128/256 can be implemented in a similar manner.

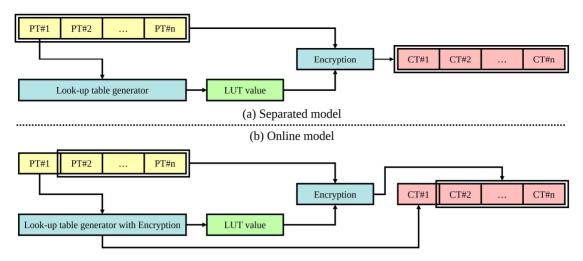

The implementation outlined in [Table 3-2] pertains to a fixed-key scenario, assuming that the secret key remains unchanged. The implementation utilizes the LDI instruction to load predefined values, meaning that if the key varies, these values must also be adjusted. Therefore, in environments where the key changes, this implementation is not feasible. Additional modifications are required to accommodate key variability, as illustrated in [Figure 3-5].

[Figure 3-5] Two implementation scenarios for the variable key model

The scenario of generating precomputed values while processing the first block can be divided into two cases. The first case involves generating only the precomputed values without encrypting the first block, corresponding to [Figure 3-5] (a). In this case, only the first 8 rounds are executed to generate the precomputed values, and then the computation halts. Once these values are generated, all blocks, including the first, can be precomputed. This approach is referred to as the "separated model."

The second case involves generating the precomputed values while simultaneously processing the first block to completion, as shown in [Figure 3-5] (b). This is referred to as the "online model." The advantage of the online model is that it avoids repeating the initial 8 rounds for the first block. However, it has the drawback of increased code complexity. Even in the variable-key scenario, the register allocation remains largely unchanged from [Figure 3-4]. However, due to the need to load the precomputed table, the address of the table is stored in registers R28 and R29, which are then used as the Υ pointer register. In the case of CHAM - 128/128and CHAM-128/256, the temporary values that were previously stored in R28 and R29 are moved to R2 and R3, allowing R28 and R29 to function as the Y pointer register for table access.

Assuming that the key changes, the first block of the input plaintext cannot undergo precomputation. Consequently, standard encryption must be performed for the first block. During this process, there is a need to store precomputed values, which will later be used for precomputation. In the proposed CHAM scheme, there are five points at which precomputed values are called. As a result, when encrypting the first block, five values must be stored to enable precomputation for subsequent blocks. Since CHAM-64/128 uses 16-bit words, five values require storing 10 bytes. In the case of CHAM-128/128 and CHAM-128/256, which use 32-bit words, double the storage—20 bytes—is required.

Once the encryption of the first block is complete, precomputed values can be used for subsequent blocks. From this point forward, the initial eight rounds can be rapidly processed using the precomputation technique outlined in the code provided in [Table 3-2].

#### 3.1.4 Alternative Implementation: Furious CHAM

The total round keys for CHAM-64/128 amount to 32 bytes, and they are reused over 88 rounds. Upon reviewing the register allocation plans in [Figure 3-4] (a), it is evident that several registers remain unused during the implementation of CHAM-64/128. Given the structural characteristic of CHAM, where round keys are reused across rounds, preloading the round keys could reduce the number of load operations, thereby enhancing computational efficiency. This optimized approach is termed "Furious CHAM."

With 16 registers available, it becomes possible to preload half of the round keys (16 bytes out of the total 32 bytes). This allows the omission of round key loads for 40 of the 80 rounds, excluding the initial 8 rounds. Since each round involves the loading of 2 bytes of round keys, omitting 80 LD instructions corresponds to a savings of 160 cycles.

[Figure 3-6] Register allocation plan for furious CHAM

To implement Furious CHAM, a new register allocation plan is proposed, as outlined in [Figure 3-5] (a) and (b). In the fixed-key scenario at [Figure 3-5] (a), only the plaintext and round key pointers are required, allowing the free use of the Y register (R28, R29). Additionally, since R28 and R29 are not callee-saved registers, the need for PUSH and POP operations is eliminated, providing a further efficiency advantage.

In the variable-key scenario at [Figure 3-5] (b), a similar register allocation is applied, but the storage location of the plaintext differs. In the fixed-key scenario, the precomputed values remain constant, allowing the use of the LDI instruction, which is one cycle faster than the LD instruction. However, LDI can only be used with

registers R16 to R31, so plaintext was stored in R18 to R25. In the variable-key scenario, since the precomputed values cannot be fetched via LDI and must be accessed via LD, this constraint does not apply.

Nonetheless, even when using LD, it is possible to maintain the same register allocation. The reason for altering the plaintext registers more precisely lies in the need to preserve the pointer value passed as a parameter. Unlike the fixed-key scenario, the variable-key scenario requires an additional pointer to store the precomputed values (table pointer). Since the parameter pointers are stored starting at R24 and R25, the third pointer is stored in R20 and R21. If the plaintext pointer is moved to X or Z and values are loaded as in the fixed-key scenario, there is a risk of losing the table pointer stored in R20 and R21. While the use of MOVW, PUSH, and POP instructions could prevent this, it would result in additional cycle costs, making the alternative register allocation plan more efficient.

Although it is possible to load the round keys before the plaintext, this approach is less efficient because round keys require more registers than plaintext. Therefore, using MOVW or PUSH and POP instructions would be unavoidable in that case.

# 3.2 TinyJAMBU with Reverse Bitwise Shift

#### 3.2.1 Reverse Bitwise Shift

TinyJAMBU exhibits a high dependency on keyed permutations, as demonstrated in [Table 3-3], where the number of keyed permutations performed at each stage is indicated.

[Table 3-4] presents the pseudocode of the keyed permutations. It can be observed that when generating t2, t3, and t4, the same

[Table 3-3] Number of keyed permutations each step in tinyJAMBU

| Step                        | Key length  |             |             |  |

|-----------------------------|-------------|-------------|-------------|--|

|                             | 128-bit     | 192-bit     | 256-bit     |  |

| Initialization: Key setup   | 1,024       | 1,152       | 1,280       |  |

| Initialization: Nonce setup | 640         | 640         | 640         |  |

| Processing associated data  | 640         | 640         | 640         |  |

| Encryption/Decryption       | 1,024       | 1,152       | 1,280       |  |

| Finalization                | 1,024 / 640 | 1,152 / 640 | 1,280 / 640 |  |

state block is used, and it is shifted in the same direction. Since each state block of TinyJAMBU consists of 32 bits, it occupies four registers on the AVR processor. In the pseudocode of [Table 3-4], the  $s_2$  state block undergoes shifts of 6, 21, and 27 times, respectively.

[Table 3-4] Pseudocode for keyed permutation(<<n: bitwise left shift n times, >>n: bitwise right shift n times, |: bitwise OR, &: bitwise AND, ^: bitwise XOR, ~: bitwise NOT)

| Input                                                     | Input: State $s_0$ , $s_1$ , $s_2$ , $s_3$ (32-bit each), Key $k$ , Round $n$ |  |  |  |  |  |

|-----------------------------------------------------------|-------------------------------------------------------------------------------|--|--|--|--|--|

| Output: State $s_0$ , $s_1$ , $s_2$ , $s_3$ (32-bit each) |                                                                               |  |  |  |  |  |

| 1:                                                        | StateUpdate( $s_0$ , $s_1$ , $s_2$ , $s_3$ , $k$ , $n$ )                      |  |  |  |  |  |

| 2:                                                        | for $i = 0$ to $n$                                                            |  |  |  |  |  |

| 3:                                                        | $t_1 = (s_1 >> 15)   (s_2 << 17)$                                             |  |  |  |  |  |

| 4:                                                        | $t_2 = (s_2 >> 6)   (s_3 << 26)$                                              |  |  |  |  |  |

```

t_3 = (s_2 >> 21) | (s_3 << 11)

5:

t_4 = (s_2 > 27) | (s_3 < < 5)

6:

feedback = s_0^t_1^(~(t_2\&t_3))^t_4^k

7:

8:

s_0 = s_1

s_1 = s_2

9:

s_2 = s_3

10:

s_3 = feedback

11:

12:

end for

```

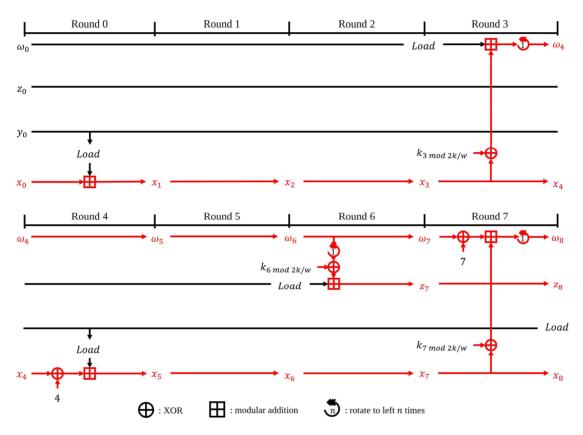

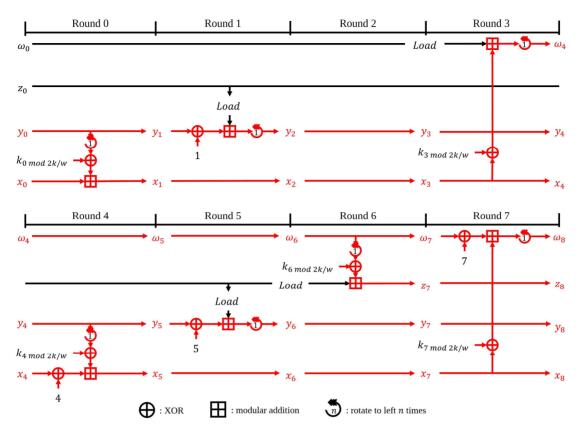

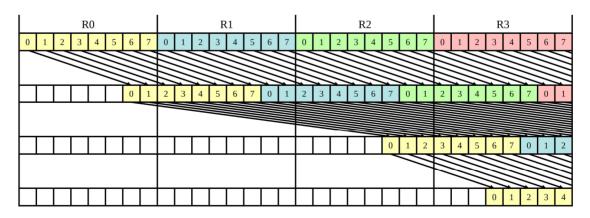

However, by utilizing the values stored in the registers, as shown in [Figure 3-4], a total of 27 shifts can be reduced to 6, 15, and 6 shifts, respectively. Consequently, the required size for  $s_2$  during computation is 26 bits, 11 bits, and 5 bits, respectively. By reusing the values left in the registers, it becomes possible to reduce the number of shifts compared to the reference implementation, leading to a more efficient computation.

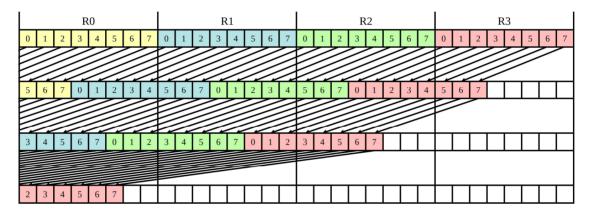

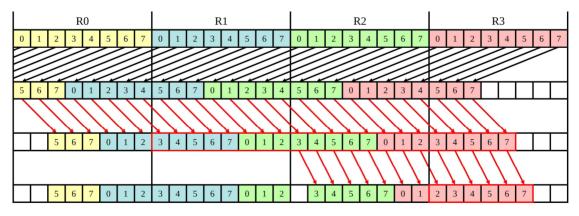

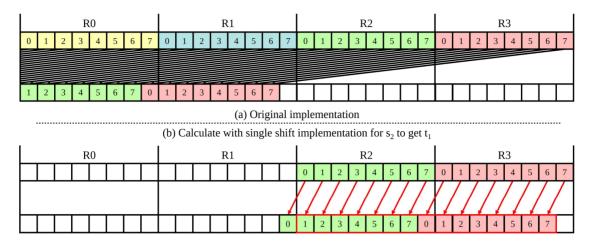

[Figure 3-7] S<sub>2</sub> state computation structure using AVR assembly instructions

Additionally, if the 8-bit operations of the AVR processor's registers are utilized, the number of shifts can be further minimized. In the second stage of [Figure 3-4], the remaining 11 bits are stored across R0, R1, and R2, with only the most significant bit of R2 being used. Thus, instead of shifting 15 times to obtain 11 bits, shifting once in the opposite direction allows the required 11 bits to be retained in R0 and R1. Similarly, the final 5 bits can be found by shifting twice in the opposite direction, as only the second bit of R1 is needed. Therefore, by reversing the direction of the shifts, as illustrated in [Figure 3-7], all necessary values can be obtained with 6 shifts in the first stage, 1 shift in the second, and 2 shifts in the third, resulting in a total of 9 shifts to complete the computation of the s<sub>2</sub> block. [Figure 3-7] also shows that the red outline values are the same as the original results.

[Figure 3-8] Proposed RBS applied to s<sub>2</sub> state calculation

The s<sub>3</sub> state block can be processed similarly. However, unlike s<sub>2</sub>, s<sub>3</sub> is shifted to the right, with the shift count decreasing in later stages. Since some values may already be lost in the early stages due to the large number of shifts, the computation proceeds in reverse order. Typically, as shown in [Figure 3-8], 5, 6, and 15

shifts are required, totaling 26 shifts.

By reversing the direction of the shifts, as done with the s<sub>2</sub> block, the number of shifts can be reduced which described at [Figure 3-9]. Specifically, the first stage proceeds with 5 shifts as usual, while the second stage, which requires 21 bits, can be obtained by shifting twice in the opposite direction and utilizing the values from R1, R2, and R3. In the final stage, which requires 6 bits, the values in R2 and R3 are shifted once in the opposite direction, and only the value from R3 is used. Similarly, the values indicated by the red line in [Figure 3-9] are the same as the existing results at [Figure 3-8].

[Figure 3-9] S<sub>3</sub> state flow with AVR assembly implementation

[Figure 3-10]  $S_3$  state calculation with RBS technique applied The temporary value  $t_1$  is generated using the  $s_1$  and  $s_2$  state

blocks, which are not involved in the generation of other temporary values. Thus, a separate implementation is performed to generate this value. The  $s_1$  block undergoes a 15-bit right shift, leaving the upper 17 bits intact. By using a RBS implementation, 24 bits from  $s_1$  can be loaded, and a single RBS will yield the required value, as illustrated in [Figure 3-10] (a) and (b). [Figure 3-10] (a) represents the implementation using the conventional method, while [Figure 3-10] (b) shows the implementation with the RBS applied. The section marked with the red line in [Figure 3-10] (b) demonstrates that the result matches the output of [Figure 3-10] (a).

[Figure 3-11] Operation process with the previous s<sub>1</sub> state block operation and RBS applied

For  $s_2$ , a 17-bit left shift is performed to retain the lower 15 bits. This can be implemented without Reverse Bitwise Shifting by loading only the lower 16 bits and shifting once to the left to obtain the desired value, as shown in [Figure 3-11] (a) and (b). In [Figure 3-11] (a), the operation is performed by shifting s2 15 times, whereas in [Figure 3-11] (b), the result is obtained by shifting in the same direction but only once. Although the number of shifts

differs, it can be observed that both yield identical computation results.

[Figure 3-12] Operate  $s_2$  state block with single shift

By employing reverse bitwise shifts, the number of required shifts in the original TinyJAMBU can be drastically reduced, even more than the method of reusing accumulated values. The differences in shift counts between the various implementations are summarized in [Table

[Table 3-5] Number of shifts for each implementation

| Case                | Reference | Assembly | RBS |

|---------------------|-----------|----------|-----|

| s <sub>1</sub> >>15 | 15        | 15       | 6   |

| s <sub>2</sub> <<17 | 17        | 17       | 1   |

| <sub>S2</sub> >>6   | 6         | 6        | 2   |

| s <sub>2</sub> >>21 | 21        | 15       | 5   |

| s <sub>2</sub> >>27 | 27        | 6        | 2   |

| s <sub>3</sub> >>5  | 5         | 5        | 1   |

| s <sub>3</sub> >>11 | 11 | 6  | 1 |

|---------------------|----|----|---|

| s <sub>3</sub> >>26 | 26 | 15 | 1 |

3-5].

3.2.2 Register Scheduling, Instructions Used and Implementation

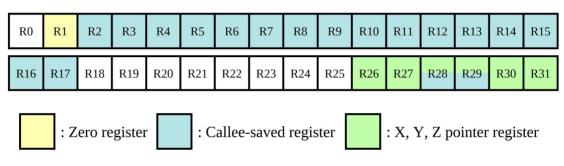

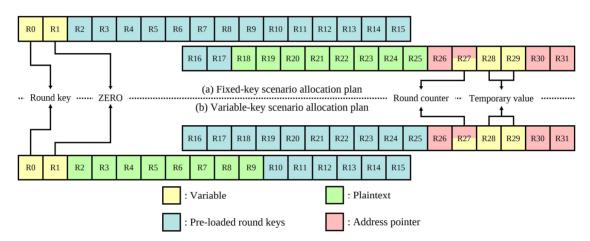

To implement the proposed TinyJAMBU, a register allocation plan, as illustrated in [Figure 3-13], is devised.

[Figure 3-13] Register allocation plan for RBS TinyJAMBU

Registers R2, R3, R4, and R5 are assigned to store the computation result state variables, while registers R6 through R13 are allocated for storing the input state variables. Registers R14, R15, R16, and R17 are designated as temporary registers to hold intermediate values during the computation. Additionally, registers R18 through R22 are used for storing key values, and registers R28 through R31 are allocated for storing pointer addresses. The types of instructions used in the implementation can be found in [Table 3-6].

[Table 3-7] presents the source code implementation of a keyed permutation that incorporates reverse bitwise shifts. The code includes only the portions where  $t_1$ ,  $t_2$ ,  $t_3$ , and  $t_4$  are generated during

[Table 3-6] List of instructions used in implementation for TinyJAMBU in alphabetical order

| Mnemonic | Operands | Description                       | Operation                                                            |

|----------|----------|-----------------------------------|----------------------------------------------------------------------|

| ADD      | Rd, Rr   | Add without Carry                 | Rd←Rd+Rr                                                             |

| CLR      | Rd       | Clear Register                    | Rd←Rd⊕Rd                                                             |

| COM      | Rd       | One's Comeplement                 | Rd←\$FF−Rd                                                           |

| EOR      | Rd, Rr   | Exclusive OR                      | Rd←Rd⊕Rr                                                             |

| LDD      | Rd, Y+q  | Load Indirect with  Displacement  | Rd←(Y+q)                                                             |

| LDD      | Rd, Z+q  | Load Indirect with Displacement   | Rd←(Z+q)                                                             |

| LSL      | Rd       | Logical Shift Left                | $Rd(n+1) \leftarrow Rd(n)$ $Rd(0) \leftarrow 0$ $C \leftarrow Rd(7)$ |

| MOVW     | Rd, Rr   | Copy Register Word                | Rd+1:Rd←Rr+1:Rr                                                      |

| OR       | Rd, Rr   | Logical OR                        | Rd←Rd v Rr                                                           |

| POP      | Rd       | Pop Register from Stack           | Rd←STACK                                                             |

| PUSH     | Rr       | Push Register on Stack            | STACK←Rr                                                             |

| ROL      | Rd       | Rotate Left Through<br>Carry      | $Rd(n) \leftarrow Rd(n+1)$ $Rd(7) \leftarrow 0$ $C \leftarrow Rd(0)$ |

| STD      | Y+q, Rr  | Store Indirect with  Displacement | (Y+q)←Rr                                                             |

| STD      | Z+q, Rr  | Store Indirect with Displacement  | (Z+q)←Rr                                                             |

the overall keyed permutation process. Lines 1-8 cover the loading

of required values. In lines 9-12, the left shift operation for s1 is used to calculate the first part of  $t_1$ , replacing the original 15 right shifts with a single left shift. Lines 13-17 prepare for subsequent operations, a process that appears intermittently after shifting each state block.

Lines 18-19 handle the computation of the second part of  $t_1$ , where  $s_2$  is shifted left once instead of the 17 left shifts in the original method. Lines 20-25 are further preparation steps for the next operations. From lines 26-49, the front part of  $t_2$  is computed by shifting  $s_2$  six times to the right, following the original procedure.

Lines 56-75 cover the calculation of the back part of  $t_4$ , where  $s_3$  is shifted left five times. Since the initial shift of each state block remains unchanged, this step mirrors the original process. Lines 80-87 simplify the calculation of the back part of  $t_3$  by replacing the original 11 left shifts with two right shifts.

Lines 91-92 compute the back part of  $t_2$  from  $s_3$ , where the original 26 left shifts are replaced by a single right shift. Lines 94-96 compute the front part of  $t_3$ , shifting  $s_2$  left once instead of the original 21 right shifts. Finally, in lines 101-104, the front part

[Table 3-7] Implementation code of proposed TinyJAMBU (RC: round counter, RK: round key, X00~X31: plaintext, XT: temporary register, Zero: zero register)

| Line |     | Code |     | Comment    |

|------|-----|------|-----|------------|

| 1:   | LDD | R2,  | Y+0 | Load state |

| 2:   | LDD | R3,  | Y+1 |            |

| 3:   | LDD | R4,  | Y+2 |            |

| 4:   | LDD | R5,  | Y+3 |            |

| 5:  | LDD | R6, | Y+5  |                                                              |

|-----|-----|-----|------|--------------------------------------------------------------|

| 6:  | LDD | R7, | Y+6  |                                                              |

| 7:  | LDD | R8, | Y+7  |                                                              |

| 8:  | CLR | R9  |      |                                                              |

| 9:  | LSL | R6  |      | Front $t_1$ : $s_1 >> 15 \rightarrow s_1 << 1$               |

| 10: | ROL | R7  |      |                                                              |

| 11: | ROL | R8  |      |                                                              |

| 12: | ROL | R9  |      |                                                              |

| 13: | EOR | R2, | R7   |                                                              |

| 14: | EOR | R3, | R8   |                                                              |

| 15: | EOR | R4, | R9   |                                                              |

| 16: | LDD | R6, | Y+8  |                                                              |

| 17: | LDD | R7, | Y+9  |                                                              |

| 18: | LSL | R6  |      | Rear $t_1$ : $s_2 << 17 \rightarrow s_2 << 1$                |

| 19: | ROL | R7  |      |                                                              |

| 20: | EOR | R4, | R6   |                                                              |

| 21: | EOR | R5, | R7   |                                                              |

| 22: | LDD | R6, | Y+8  |                                                              |

| 23: | LDD | R7, | Y+9  |                                                              |

| 24: | LDD | R8, | Y+10 |                                                              |

| 25: | LDD | R9, | Y+11 |                                                              |

| 26: | LSR | R9  |      | Front t <sub>2</sub> : s <sub>2</sub> >>6 (same as original) |

| 27: | ROR | R8  |      |                                                              |

| 28: | ROR | R7  |      |                                                              |

| 29: | ROR | R6  |      |                                                              |

| 30: | LSR | R9  |      |                                                              |

| 31: | ROR | R8  |      |                                                              |

| 32: | ROR | R7  |      |                                                              |

| 99. | DOD  | D.G  |      |                                                          |

|-----|------|------|------|----------------------------------------------------------|

| 33: | ROR  |      |      |                                                          |

| 34: | LSR  | R9   |      |                                                          |

| 35: | ROR  | R8   |      |                                                          |

| 36: | ROR  | R7   |      |                                                          |

| 37: | ROR  | R6   |      |                                                          |

| 38: | LSR  | R9   |      |                                                          |

| 39: | ROR  | R8   |      |                                                          |

| 40: | ROR  | R7   |      |                                                          |

| 41: | ROR  | R6   |      |                                                          |

| 42: | LSR  | R9   |      |                                                          |

| 43: | ROR  | R8   |      |                                                          |

| 44: | ROR  | R7   |      |                                                          |

| 45: | ROR  | R6   |      |                                                          |

| 46: | LSR  | R9   |      |                                                          |

| 47: | ROR  | R8   |      |                                                          |

| 48: | ROR  | R7   |      |                                                          |

| 49: | ROR  | R6   |      |                                                          |

| 50: | MOVW | R14, | R6   |                                                          |

| 51: | MOVW | R16, | R8   |                                                          |

| 52: | LDD  | R10, | Y+12 |                                                          |

| 53: | LDD  | R11, | Y+13 |                                                          |

| 54: | LDD  | R12, | Y+14 |                                                          |

| 55: | LDD  | R13, | Y+15 |                                                          |

| 56: | LSL  | R10  |      | Rear t <sub>4</sub> : s <sub>3</sub> <<5 (same as origin |

| 57: | ROL  | R11  |      |                                                          |

| 58: | ROL  | R12  |      |                                                          |

| 59: | ROL  | R13  |      |                                                          |

| 60: | LSL  | R10  |      |                                                          |

| 61: | ROL  | R11 |                                              |

|-----|------|-----|----------------------------------------------|

| 62: | ROL  | R12 |                                              |

| 63: | ROL  | R13 |                                              |

| 64: | LSL  | R10 |                                              |

| 65: | ROL  | R11 |                                              |

| 66: | ROL  | R12 |                                              |

| 67: | ROL  | R13 |                                              |

| 68: | LSL  | R10 |                                              |

| 69: | ROL  | R11 |                                              |

| 70: | ROL  | R12 |                                              |

| 71: | ROL  | R13 |                                              |

| 72: | LSL  | R10 |                                              |

| 73: | ROL  | R11 |                                              |

| 74: | ROL  | R12 |                                              |

| 75: | ROL  | R13 |                                              |

| 76: | PUSH | R10 |                                              |

| 77: | PUSH | R11 |                                              |

| 78: | PUSH | R12 |                                              |

| 79: | PUSH | R13 |                                              |

| 80: | LSR  | R13 | Rear $t_3$ : $s_3 <<11 \rightarrow s_3 >> 2$ |

| 81: | ROR  | R12 |                                              |

| 82: | ROR  | R11 |                                              |

| 83: | ROR  | R10 |                                              |

| 84: | LSR  | R13 |                                              |

| 85: | ROR  | R12 |                                              |

| 86: | ROR  | R11 |                                              |

| 87: | ROR  | R10 |                                              |

| 88: | PUSH | R10 |                                              |

| 89:  | PUSH | R11  |     |                                                 |

|------|------|------|-----|-------------------------------------------------|

| 90:  | PUSH | R12  |     |                                                 |

| 91:  | LSR  | R11  |     | Rear $t_2$ : $s_3 < < 26 \rightarrow s_3 >> 1$  |

| 92:  | ROR  | R10  |     |                                                 |

| 93:  | OR   | R9,  | R10 |                                                 |

| 94:  | LSL  | R15  |     | Front $t_3$ : $s_2 >> 21 \rightarrow s_2 << 1$  |

| 95:  | ROL  | R16  |     |                                                 |

| 96:  | ROL  | R17  |     |                                                 |

| 97:  | POP  | R12  |     |                                                 |

| 98:  | POP  | R11  |     |                                                 |

| 99:  | POP  | R10  |     |                                                 |

| 100: | OR   | R10, | R17 |                                                 |

| 101: | LSL  | R16  |     | Front: $t_4$ : $s_2 >> 27 \rightarrow s_2 << 2$ |

| 102: | ROL  | R17  |     |                                                 |

| 103: | LSL  | R16  |     |                                                 |

| 104: | ROL  | R17  |     |                                                 |